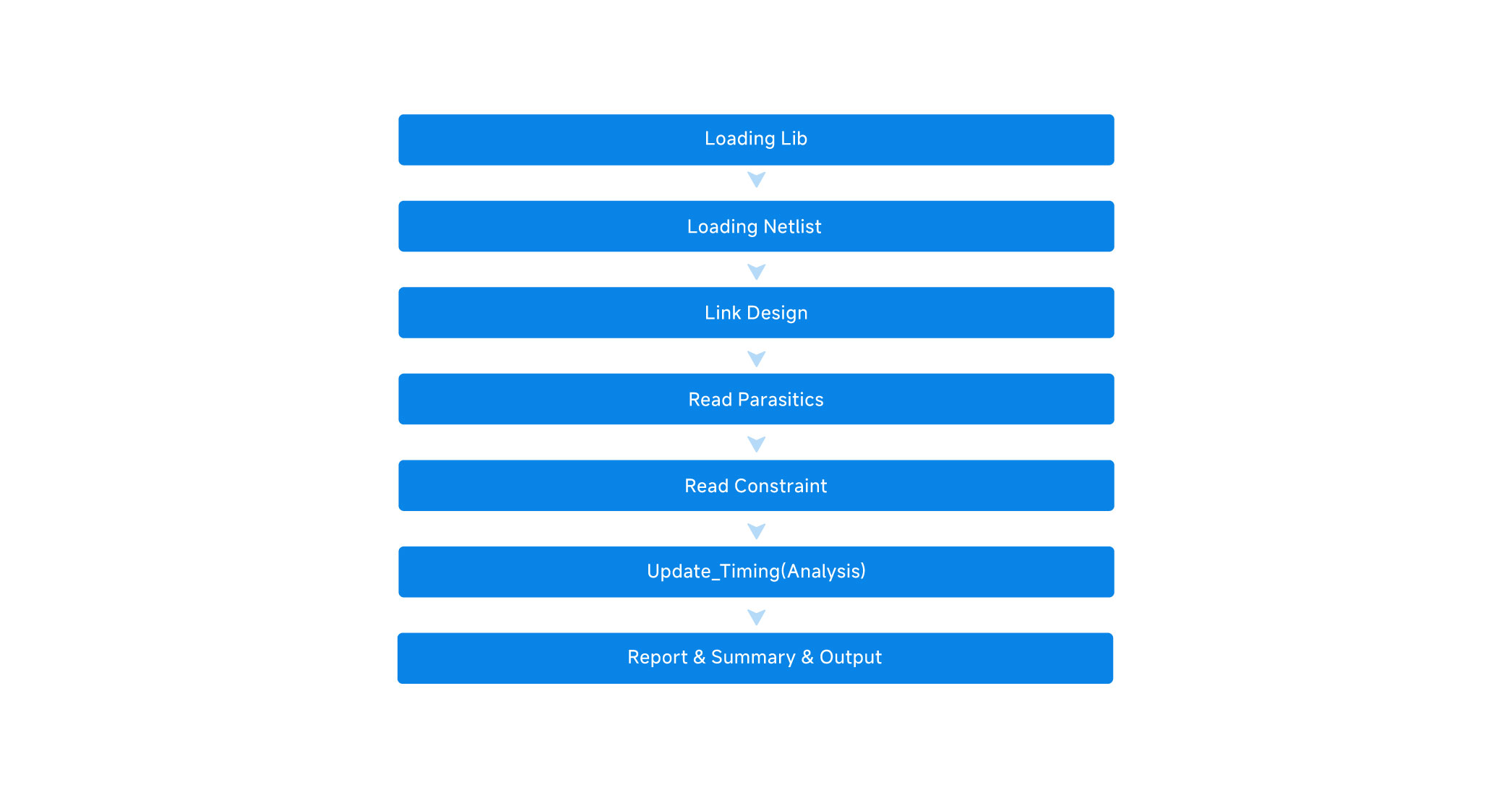

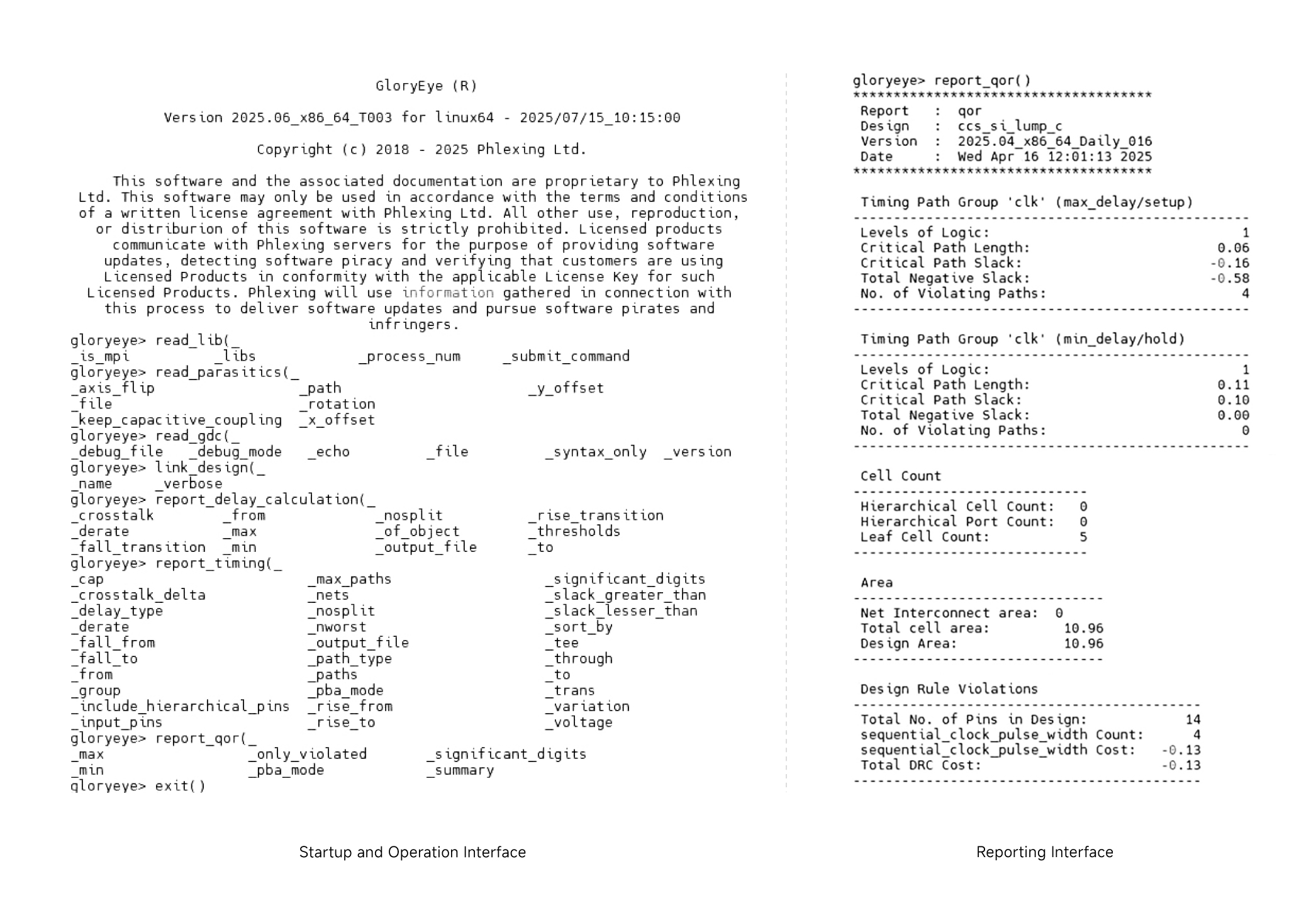

GloryEye is a high-precision static timing analysis tool integrating timing, signal integrity, and power analysis. It features full design constraint parsing and industry-leading silicon data correlation. With innovative variation-aware modeling and support for NLDM and CCS timing models, its intelligent multi-core parallel engine and efficient memory management handle ultra-large designs. GloryEye supports both flatten and hierarchy analysis flows, providing end-to-end timing verification from RTL to GDSII for faster, reliable timing closure.

· 3DIC Static Timing Analysis:

Supports parasitic extraction and back-annotation for 3DIC structures, leveraging hierarchical signoff flows to address large-scale timing challenges.

· Multi-Mode Multi-Corner Parallel Analysis:

Distributed multi-scenario engine enables concurrent timing verification for multi-voltage, multi-mode, and multi-corner conditions via intelligent threading optimization, enhancing efficiency from block to full-chip level.

· Partitioned Timing Signoff:

For ultra-large designs, allows splitting into independent parallel signoff tasks to overcome data scale and runtime bottlenecks, automating the flow to accelerate design iterations.

Zhejiang public network security 33010802011331

Zhejiang public network security 33010802011331