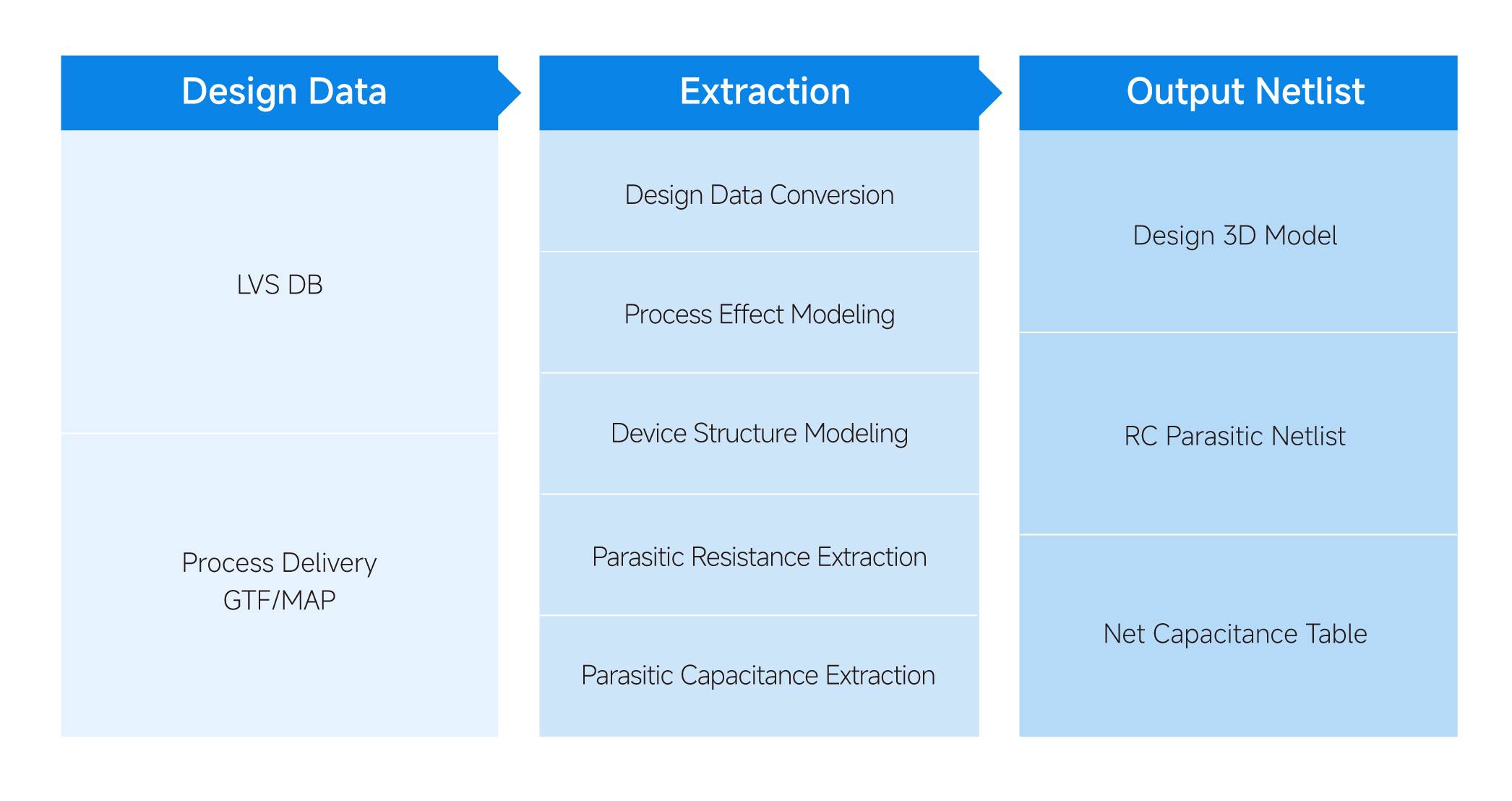

GloryEX3D efficiently solves Maxwell’s partial differential equations using the random walk method. This solver is suitable for parasitic parameter extraction of complex 3D structures and offers excellent parallel scalability. It is widely applicable to standard cell and IP module parasitic parameter solving, particularly for analyzing parasitic effects in critical chip paths. The tool ensures extraction accuracy for key nodes and parameters in advanced processes, with leading industry performance in solving efficiency and parallel scaling. Its accuracy meets foundry requirements for parasitic parameter modeling. By precisely modeling device-critical features like Fin structures and Epi layers, GloryEX3D effectively characterizes the electrical properties of parameterized cells and standard cells, providing a high-reliability parasitic parameter foundation for chip design.

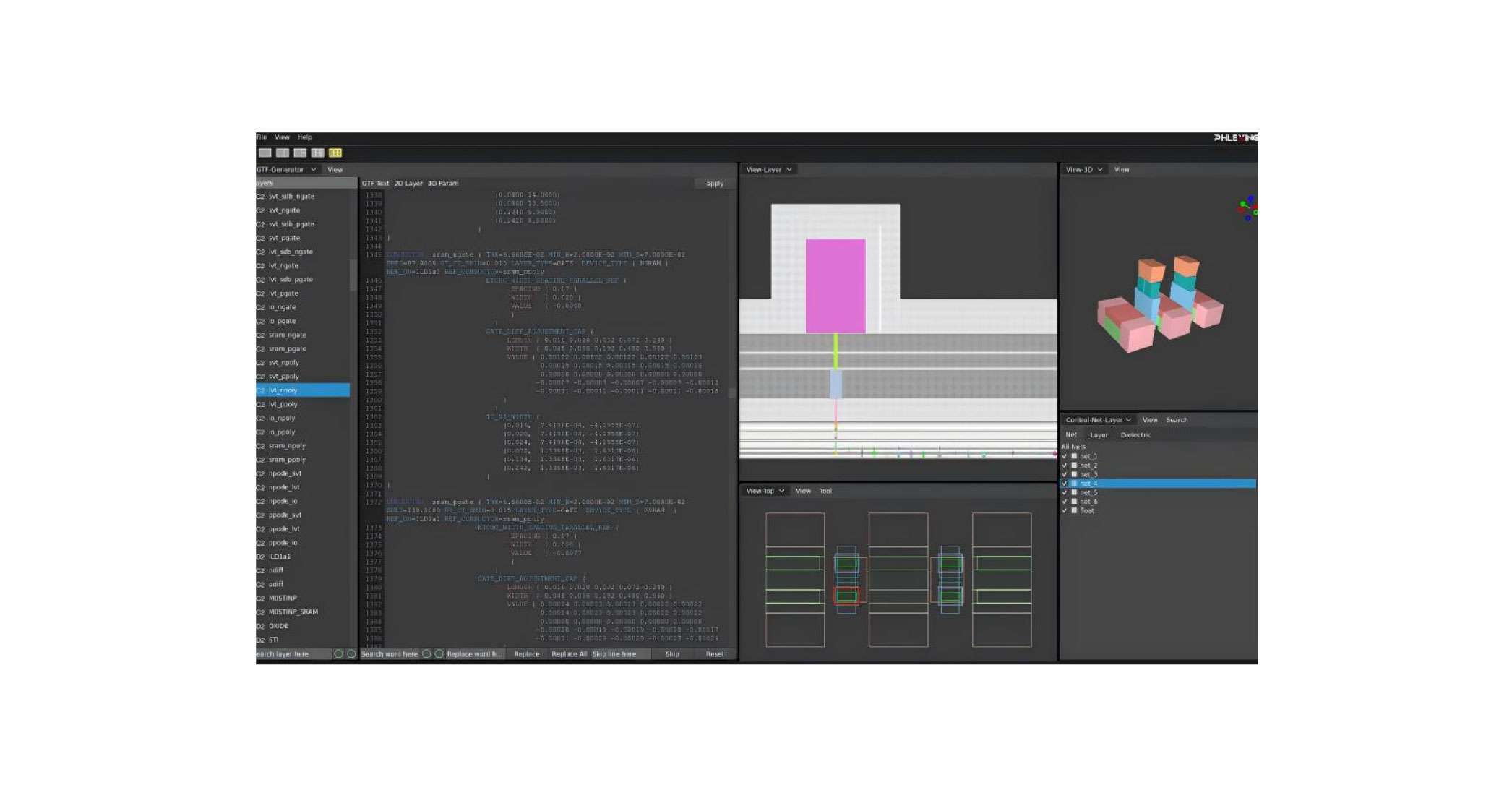

Powerful GUI and Unique Visual Modeling:

GloryEX3D provides graphical Tech File development capabilities with an intuitive "edit-and-preview" interface. Unlike traditional workflows, it integrates Viewer and Tech File Editor modules, allowing real-time visualization of layer stacks and device morphologies during Tech File development. The system auto-generates corresponding 3D models, enabling immediate validation. Command prompts for editing templates further reduce Tech File complexity and boost development efficiency.

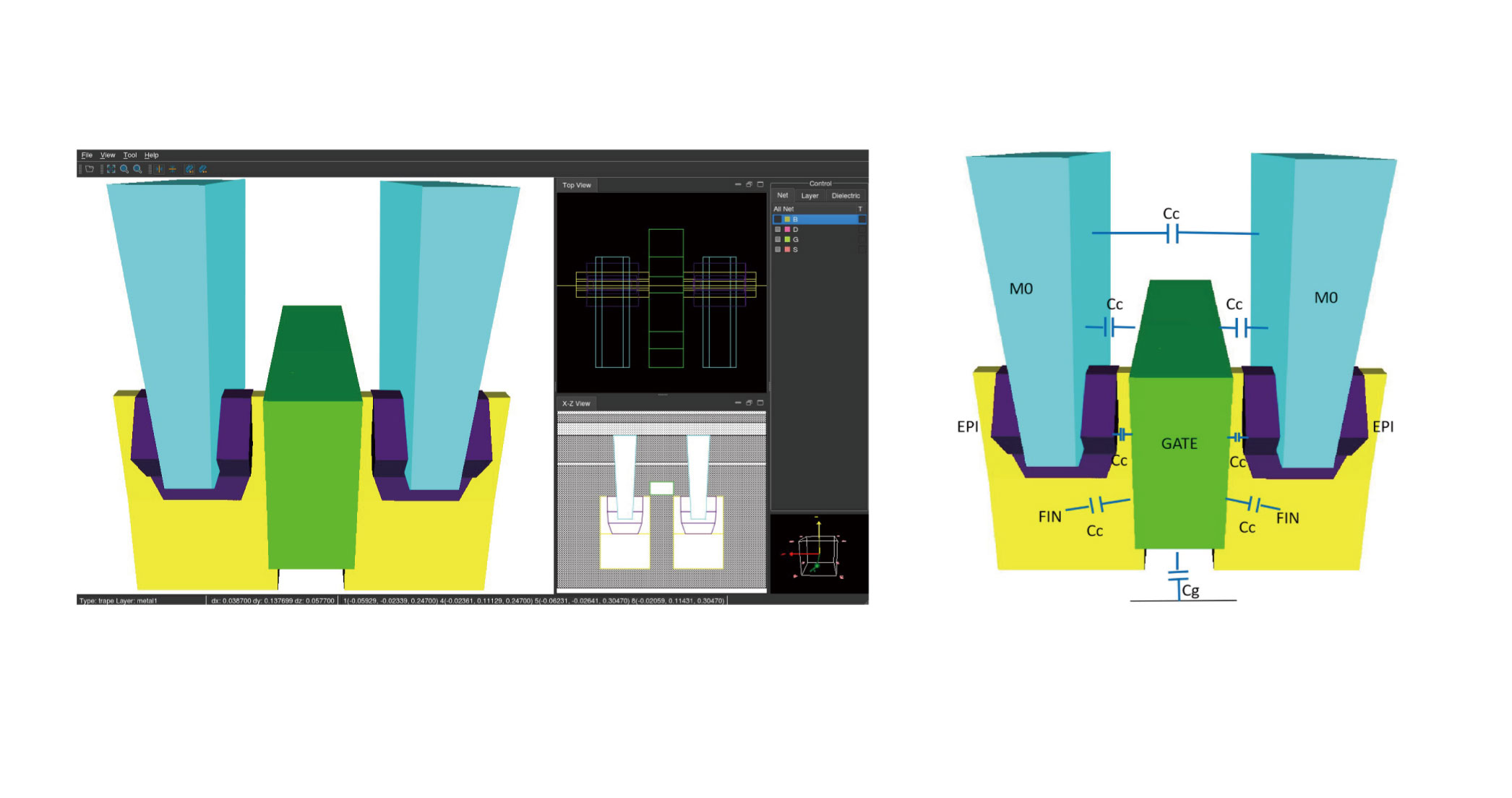

Precision Modeling for Advanced Process Structures:

GloryEX3D employs the GloryEX Technology File (GTF) as its standard technology file. The GTF can describe the electrical characteristics of different process layers, such as resistivity and dielectric constant, enabling precise modeling of manufacturing process effects. It supports an accuracy of up to 0.1nm, allowing for accurate parasitic parameter extraction in advanced processes like FinFET. Furthermore, GloryEX3D is equipped with a powerful graphics processing engine. Its flexible graphical operation commands facilitate the construction of complex layouts, ensuring precise modeling capabilities.

High-Precision, High-Efficiency 3D Solver:

Combines advanced algorithms with high-performance parallel computing to rapidly extract capacitance and resistance for complex structures. It accurately simulates actual process effects and captures subtle parasitic variations, enhancing PDK development efficiency. Supports cross-scale modeling from BEOL and parameterized cells to standard cells and SRAM chips, enabling precise analysis and optimization across hierarchies. Validated by leading semiconductor companies, it is a trusted solution for advanced node parasitic extraction.

Zhejiang public network security 33010802011331

Zhejiang public network security 33010802011331