GloryEX delivers signoff-precision, high-performance RC extraction for the most complex chip designs, spanning digital, analog, SoC and 3DIC heterogeneous integration. It delivers the precision required for final signoff while meeting the demanding capacity and speed needs of modern semiconductor development.

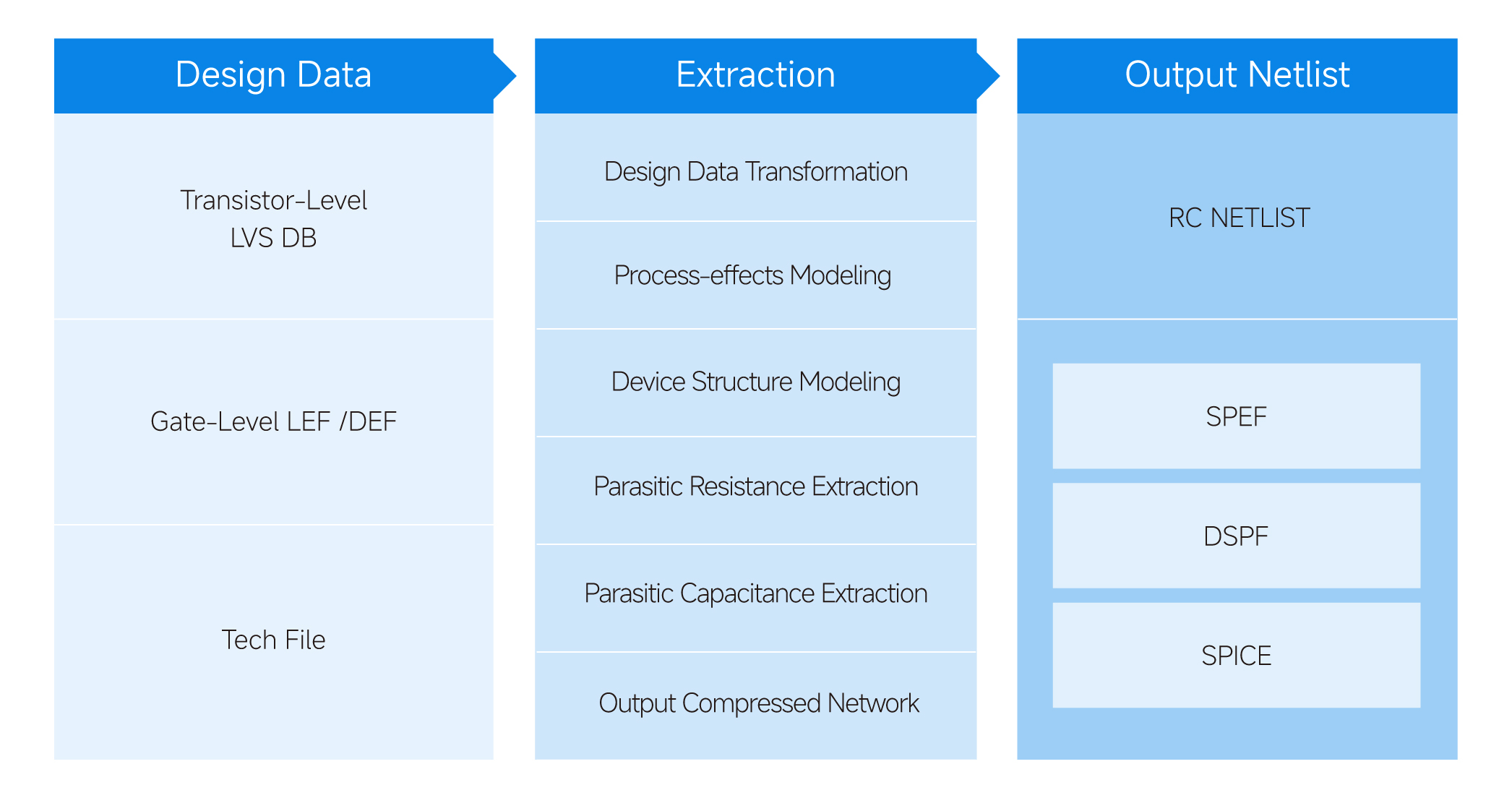

In digital design, GloryEX supports gate-level parasitic extraction for billion-gate ultra-large-scale designs. It seamlessly integrates with mainstream backend design platforms and collaborates with other Phlexing’s signoff tools, including EM/IR, Timing, Power and more.GloryEX and other Phlexing’s tools provide an efficient and consistent one-stop signoff solution.

For analog applications, the tool supports importing third-party LVS database. Combined with the GloryEX3D high-precision calculation engine, it accurately models transistor structures under advanced process technologies, enabling transistor-level high-accuracy parasitic extraction.

When it comes to 3DIC heterogeneous integration, GloryEX supports face-to-face wafer stacking structures, providing cross-chip capacitance extraction, TSV modeling, and full-link extraction capabilities adapted to heterogeneous integration workflows, meeting RC analysis needs for advanced packaging designs.

Furthermore, GloryEX supports modeling of various advanced process effects, including OPC (Optical Proximity Correction), CMP (Chemical Mechanical Planarization) effects, Low-k Damage effects, and double/multiple patterning effects. Its accuracy has been certified by leading domestic and international foundries and validated through tape-outs, ensuring reliability for designs across different process nodes.

Ultra-Large-Scale Parallel Extraction Computing:

Accelerate billion-gate chip parasitic extraction through an adaptive partitioning parallel architecture, dramatically reducing turnaround time for large-scale designs.

Multi-Corner Parallel Extraction (MCPE):

Enables parallel extraction across multiple process corners, improving full-chip parasitic parameter extraction efficiency by over 35%.

Virtual Metal Fill (VMF) Evaluation and Optimization:

Built-in VMF functionality allows accurate quantification of metal fill impact on parasitic capacitance without additional fill operations, drastically reducing iterative optimization time.

3DIC Cross-Foundry Data Integration:

Compatible with mainstream foundry 3DIC Bonding GTF formats, enabling seamless integration of multi-foundry CAPTAB databases and overcoming data unification challenges in cross-foundry collaboration.

Signoff-Level Precision Assurance:

Deeply integrated with the GloryPolaris and GloryEX 3D field solvers, it supports the precision verification loop of foundry process design kits (PDK), ensuring data reliability across various design application scenarios—from silicon data parameter-based modeling of device-level parasitic parameters and metal interconnect modeling, to foundation IP characterization, and full-chip parasitic parameter extraction.

One-Stop Signoff Flow:

Seamlessly integrates within the Phlexing signoff platform,enabling a unified workflow with GloryEye for static timing analysis, GloryBolt for EM/IR signoff,and PhyBolt for multi-physics coupling analysis, ensuring consistent accuracy and efficiency across the entire design flow.

Zhejiang public network security 33010802011331

Zhejiang public network security 33010802011331