2024-06-28

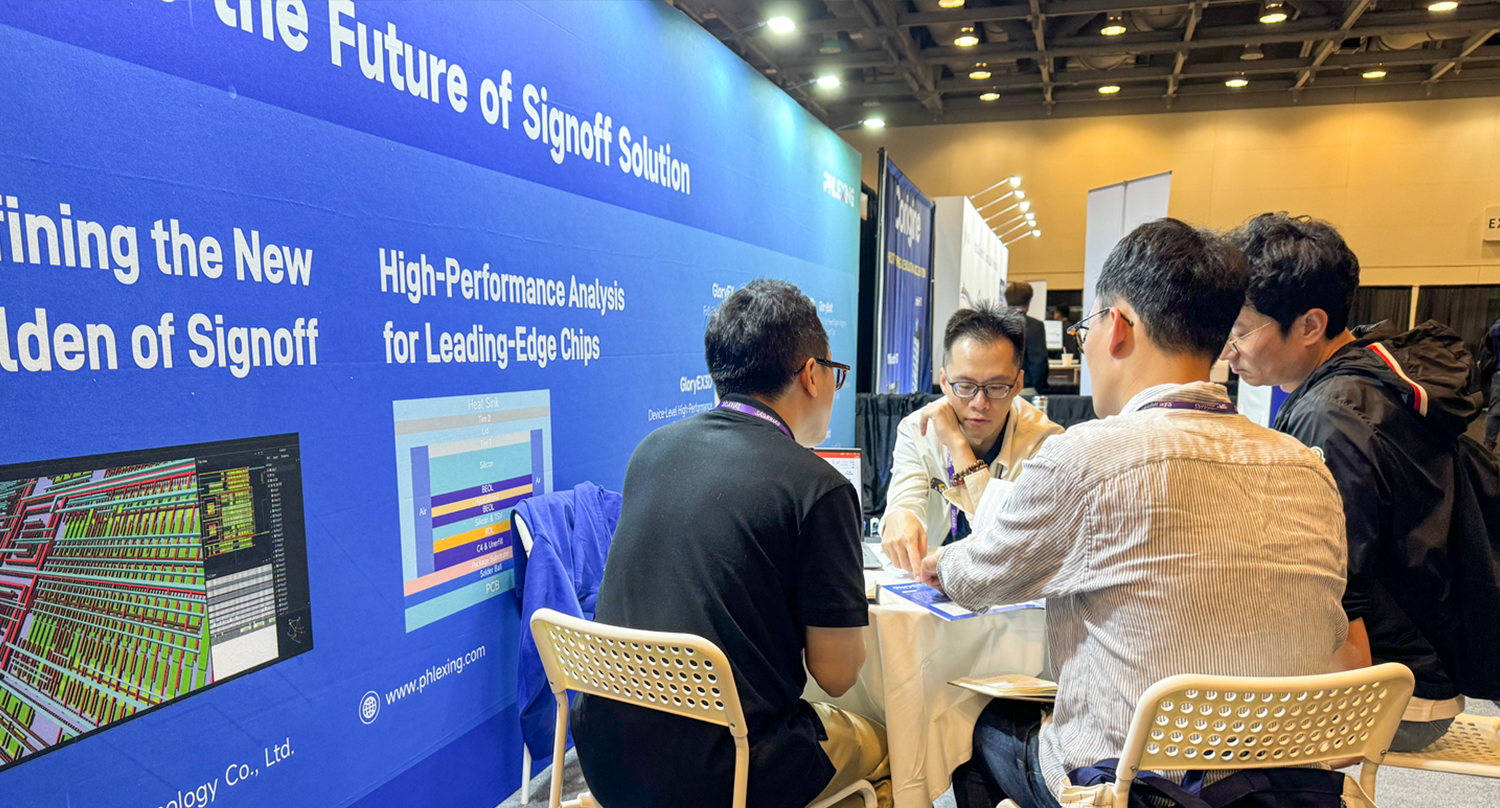

[San Francisco, June 27, 2024] —— The 61st Design Automation Conference (DAC) has successfully concluded in San Francisco. As a top event in the Electronic Design Automation (EDA) and semiconductor industry, DAC attracted engineers, designers, researchers, and industry leaders from around the world to discuss and showcase the latest technologies, tools, and market trends within the industry.

Phlexing highlighted and launched new products GloryEX3D (a high-efficiency parasitic parameter field solver at the device level) and GloryPolaris (a high-precision 3D parasitic parameter modeling tool) at this DAC. Customers have shown great interest in our 3D solutions.

GloryEX3D (A High-Efficiency Parasitic Parameter Field Solver at the Device-Level)

GloryEX3D can quickly process calculations, boasting industry-leading solution efficiency and parallel computing capacity. Its computational accuracy meets the requirements for parasitic parameter model establishment in foundry, characterizing the M1 and V0 characteristics of P-cells and Template Cells through modeling at the device level (Fin num, M0 (local interconnect)). It can be applied to high-precision extraction of small and medium-sized layouts or high-precision solution of key paths in chips, meeting signoff accuracy requirements.GloryEX3D ensures the accuracy requirements of all key nodes and parameters, supporting both advanced processes and mature (Planar MOS) processes.

GloryPolaris (A High-Precision 3D Parasitic Parameter Modeling Tool)

GloryPolaris performs 3D modeling using input data from the Foundry TD end, such as Silicon Data, Pattern, Rule, and Profile. It supports the integration of process effect modules like BEOL (Back-End-Of-Line), CMP (Chemical-Mechanical Polishing), etch-loading, and TSV (Through-Silicon Vias) modeling. It can be used for the precise solution of device-level parasitic capacitance and the establishment of interconnect models, with results serving as the highest accuracy Golden standard.GloryPolaris provides the highest precision parasitic parameter extraction for both advanced and mature processes (Planar MOS).

With the successful conclusion of the 2024 DAC, Phlexing will continue to increase its investment in R&D, promote innovation and application of EDA technology, and contribute more solutions to the development of the global semiconductor industry.