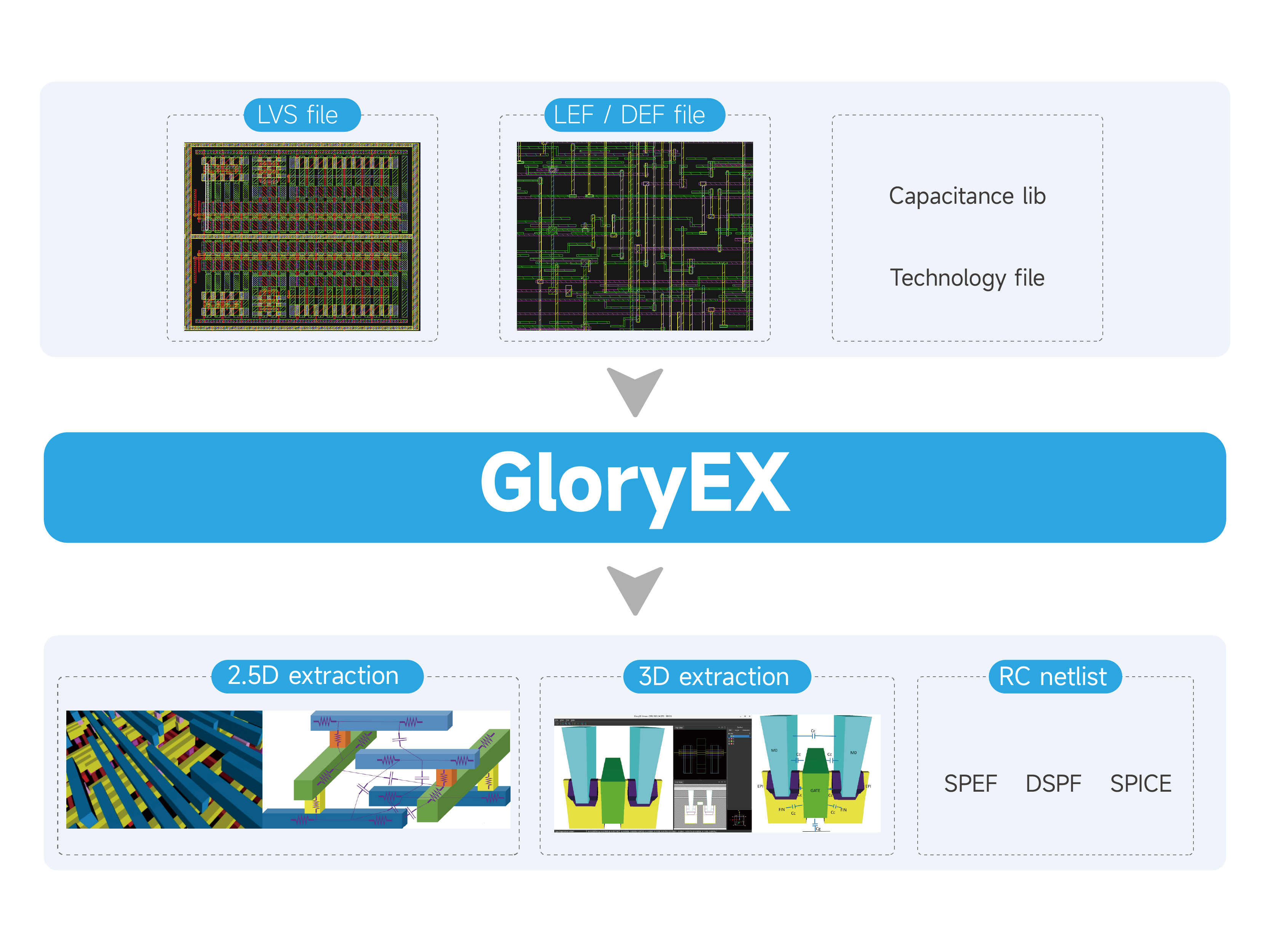

Support designs for SoC, ASIC, Memory, Custom, AMS etc.

3D extraction mode and 2.5D fast extraction mode with high accuracy

Support high accuracy extraction of BEOL, MEOL and FEOL at advanced process nodes

Offer technology modeling of complex geometric structures and different physical effects. Support technology modeling of complex device structures and parasitic parameters in advanced nodes

High-accuracy 3D technology modeling of special structures for Foundry Golden standard

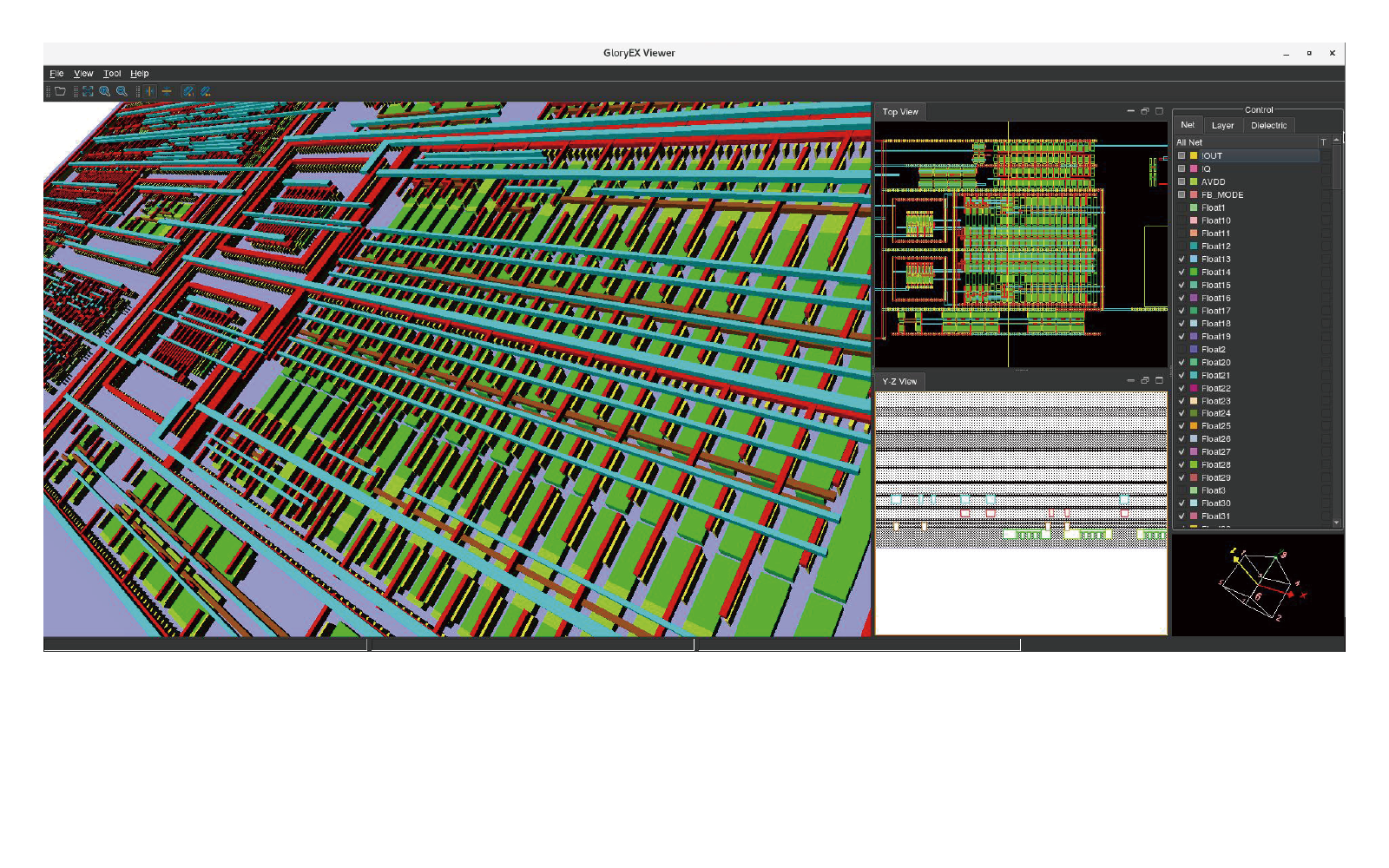

Offer 3D device structure display interface that enables developers to check modeling data and 3D configuration. Accurate characterization of conductor and dielectric parameters

Capable of multi-core parallel processing, domain partitioning, and hierarchical extraction; support rapid extraction of full-chip parameters in large-scale design

Offer large-scale and high-performance extraction at transistor-level and gate-level

Provide precise 3D capacitance solver and accurate characterization of IP library in critical nets. Significant net-list compression for faster simulation and shorter run-time

Zhejiang public network security 33010802011331

Zhejiang public network security 33010802011331